TimeServo IP Core from Atomic Rules

BittWare Partner IP TimeServo IP Core High Performance System Timer IP The TimeServo IP core by Atomic Rules is an RTL IP core that serves

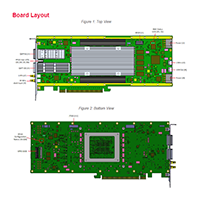

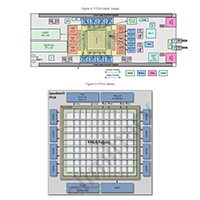

The S7t-VG6 VectorPath accelerator card offers a 7nm Achronix FPGA that is optimized for high-speed networking and fast, high-capacity memory access. Featuring a QSFP-DD (double-density) cage, the board supports up to 1x 400GbE or 4x 100GbE using the 56G PAM4-enabled Speedster®7t device. An additional QSFP port supports 2x 100GbE, and a 4x MCIO connector for expansion. Sixteen channels of GDDR6 graphics DRAM handle high-bandwidth memory requirements, providing up to 448GB/s.

The FPGA offers large logic and memory resources—up to 692K 6-input lookup tables (LUTs), and 189 Mb embedded RAM. It also provides 2,560 MLPs (machine-learning blocks).

QSFPs for 1x 400G or 6x 100G

16GB GDDR6 up to 448GB/s

7nm FPGA with 56Gbps SERDES

Craig Petrie gives a detailed explanation of the card's key features.

Generation 5.0

The HRG gives you much more detail about the card such as block diagrams, tables and descriptions.

r4 v2

Our technical sales team is ready to provide availability and configuration information, or answer your technical questions.

"*" indicates required fields

BittWare Partner IP TimeServo IP Core High Performance System Timer IP The TimeServo IP core by Atomic Rules is an RTL IP core that serves

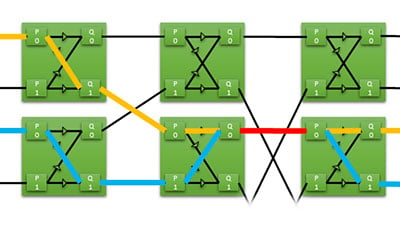

Efficient Sharing of FPGA Resources in oneAPI Building a Butterfly Crossbar Switch to Solve Resource Sharing in FPGAs The Shared Resource Problem FPGA cards usually

PCIe FPGA Card 520N-MX Stratix 10 FPGA Board with 16GB HBM2 Powerful solution for accelerating memory-bound applications Need a Price Quote? Jump to Pricing Form

Go Back to IP & Solutions UDP Offload Engine UOE IP Core for 10/25/50/100GbE Atomic Rules UDP Offload Engine (UOE) is a UDP FPGA IP