520NX PCIe Card with Intel Stratix 10 NX FPGA

PCIe FPGA Card 520NX Stratix 10 AI-optimized FPGA with HBM2 AI-Optimized for High-Bandwidth, Low-Latency AI Acceleration Obsolete Product Notice: This is an obsolete product and

TCP/IP(傳輸控制協定/互聯網協定)是用於 FPGA 的乙太網 IP 內核,它結合了傳輸層和互聯網層協定,可在互聯網或專用網路上提供可靠的端到端網路通信。

Chevin Technology 的 TCP/IP 卸載引擎是一款 FPGA 可合成乙太網 TCP/IP 伺服器/用戶端,採用精簡、快速的全 RTL 解決方案。TCP IP 核可與 10G 和 25G 乙太網 IP 核配合使用,以最少的資源在任何 FPGA 中實現可靠、高性能的連接。Chevin Technology 的 TCP/IP 核使用快速高效的邏輯進行校驗和計算,從而減輕了 TCP 協定的負載,並且很容易與其他協定集成,為開發支援 TCP 的 FPGA 應用提供了一條簡單的途徑。

該IP核針對採用AMD Virtex UltraScale+和Altera Agilex 7器件的BittWare FPGA卡。具體支援的卡列在規格下。

TCP/IP Offoad 引擎提供了一條快速創建支援 TCP 的應用程式的途徑,只需在 FPGA 端進行網路管理所需的額外資源最少。AXI4-Lite 主機介面允許控制和配置 TCP IP 核的寄存器以及用於連接和鏈路監控的統計資訊。使用者應用程式端和 MAC 透過易於使用的 AXI4-Stream 或 Avalon 介面連接到 TCP IP 核。

TCP IP 核可以配置為啟動(用戶端)或接受(伺服器)與遠端端點的 TCP 連接。一旦建立了會話,就可以通過TCP協定可靠地發送和接收數據;以 10 或 25 Gbit/s 的高持續數據速率處理校驗和插入/檢查、套接字和流量控制。用戶介面提供流控制,並管理多個連接。

支援多個同時連接,僅受可用數據包緩衝區資源的限制。打開和關閉連接由 TCP 內核處理,無需額外的軟體支援。重新傳輸由 TCP 中的控制層處理,以實現快速、輕鬆的錯誤恢復。收集所有發送和接收幀的統計資訊,以進行流量和連接分析。

TX / RX– Latency < 1 us

| 會話 | 資源 | 用法 |

|---|---|---|

| Altera Agilex F-Series | 32 | 啟用了所有功能的IA-840F卡,包括記憶體映射介面: 40k ALM, 220 M20K |

| AMD Virtex UltraScale、Zynq | 16 | 記憶體佔用小:110 BRAM + 數據包緩衝區;35000 LUT |

乙太網軟體供應商,為高端 FPGA 提供高性能、可靠的數據傳輸功能。

我們的技術銷售團隊隨時準備提供可用性和配置資訊,或回答您的技術問題。

“*”表示必填欄位

PCIe FPGA Card 520NX Stratix 10 AI-optimized FPGA with HBM2 AI-Optimized for High-Bandwidth, Low-Latency AI Acceleration Obsolete Product Notice: This is an obsolete product and

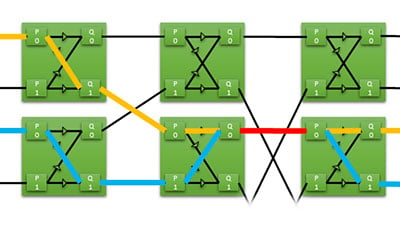

在一個API中高效共用FPGA資源 構建蝶形橫桿開關,解決FPGA中的資源分享問題 FPGA卡通常

Article Homomorphic Encryption Acceleration FPGA acceleration enables this unique solution that allows compute on encrypted data without decrypting or sharing keys Traditional Encryption Limits Encrypting