Arkville Agilex FPGAを用いたDPDKデータムーバー

BittWare WebinarArkville Intel® Agilex™ FPGA を使用した PCIe Gen4 Data Mover Webinar Atomic Rules 社のArkville IP は、最近更新され、Intel をサポートしました。Agilex

HBM2メモリを搭載したFPGAは、アルゴリズムに「コーナーターン」が含まれる場合、GPUチップよりも高速に動作します。これは、FPGAがコーナーターン操作を計算とオーバーラップさせることができるため、レイテンシーの観点から「自由」になるためです。2次元FFTを使用してこのテクニックを実証し、以下にソースコードを提供します。公平性を保つために、このコードではGPUもサポートするデータ型を使用しています。FPGAはどんなデータ型でも簡単に処理することができます。

BittWare 以前、インテルのOpenCLコンパイラを使用してFPGA用の2D FFTカーネルを作成しました。今回、そのコードをIntelのoneAPIプログラミングモデル、特にDPC++プログラミング言語を活用するように書き直しました。520N-MXカードでも 同様の性能を得ることができました。インテルは、oneAPIをGPUやFPGAを必要とするアプリケーションに最適なツールチェーンとして推進していますアクセラレーション 。

2次元FFTはFPGAのIPライブラリに含まれていることが多いため、プログラマーが自分で実装することは一般的ではありません。しかし、並列ハードウェア上での2D FFTの一般的な実装戦略には、CPUやGPUで性能の大きなボトルネックとなる「コーナーターン」または「データ転置」ステップが含まれています。

このデモで強調したのは、FPGAの実装では、計算と並行してデータの転置を行うことができるため、レイテンシーの観点からほぼ「無料」であるということです。

GPUは、GPUアーキテクチャがHBM2/GDDR6メモリに触れずに中間結果をパイプライン化するのに十分なメモリをGPU内部に持たないため、同じことができない。

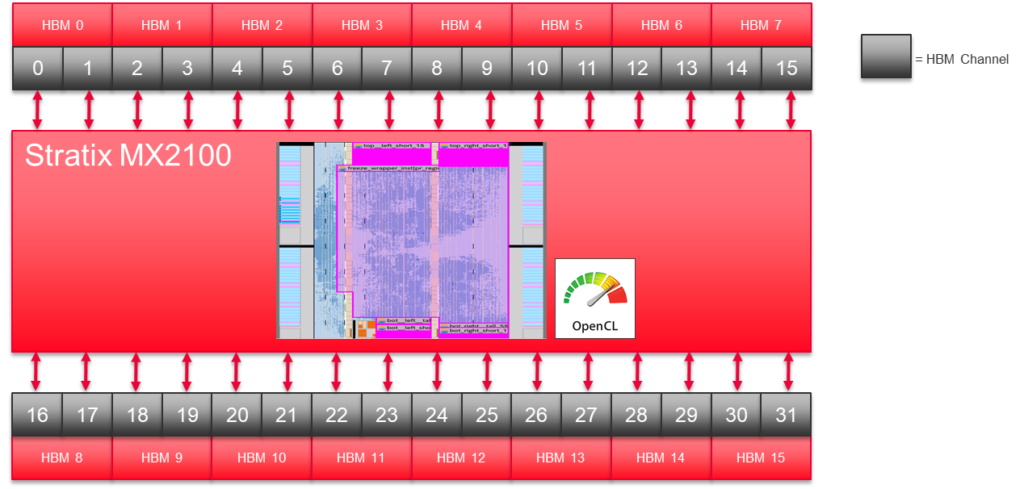

Stratix 10 MXには32個の擬似HBM2メモリチャンネルがあります。私たちの2D FFTの実装では、その半分のチャンネルを使用しています。

Stratix 10 MXには32個の擬似HBM2メモリチャンネルがあります。私たちの2D FFTの実装では、その半分のチャンネルを使用しています。

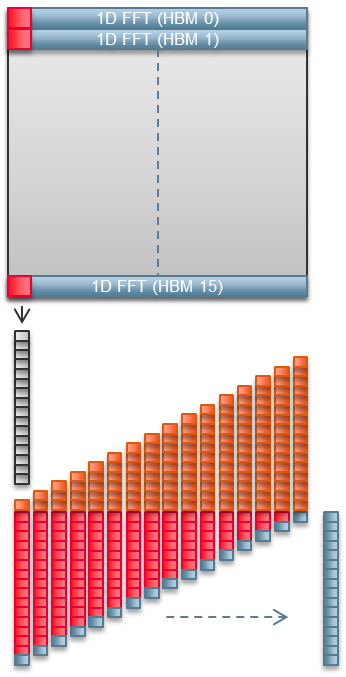

16個の1次元FFTを同じクロックサイクルで開始するわけではありません。その代わりに、1つの複素数要素ごとに開始点をずらしています。こうすることで、1次元FFTの結果をコーナーターン・ロジックにパイプライン接続することができます。

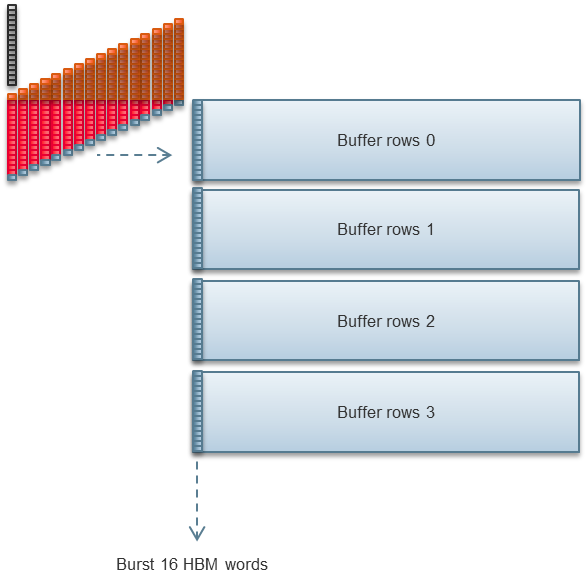

転置したデータを32バイトのチャンクでHBMに書き込めるようにするためには、4つの1次元FFTの出力を待つ必要があるのです。

BittWareの開発チームは、RTL(VerilogとVHDL)、HLS(主にC++)、OpenCL、そして今回のDPC++を使用しています。 以前、RTLとHLSを比較したホワイトペーパーを発表しました。今回のプロジェクトは、OpenCLとDPC++を比較する最初の機会でした。

FPGA用のOpenCLコードからFPGA用のDPC++への移行は簡単だったことをご報告します。FPGAとHBM2オンパッケージメモリに特有の適応は、OpenCLバージョンと非常に似ていました。 ホストコンピュータ上でのデータ移動も簡単でした。OpenCL版では試みなかったNumPyからの2次元FFTカーネル呼び出しもできました。

M20Kメモリを512枚(MX2100の12.5%)使用しています。

FPGA に実装される FFT の長さは、通常、ビットストリームのコンパイル時に設定されます。

FPGAのIPライブラリを使用するのではなく、独自の1次元FFTを実装しました。この1次元FFTは基数2で、完全にパイプライン化されています。インプレースではありません。

2D FFTの性能は、常にHBM2の帯域幅によって制限されます。したがって、私たちの焦点は、HBM2帯域幅を最大化できるアルゴリズムを見つけることです。これは、HBM2帯域幅のベンチマークを使用して、FFTの性能を正確に見積もることができるということでもあります。

同じデバイスに2つの独立したカーネルを搭載したバッチ1実装のHBM2のピーク性能は、291GBytes/Secです。パイプライン/バッチ処理時には、337GBytes/Secのピーク帯域幅が可能です。

私たちは、2D FFTをOpenCLバージョンからoneAPIに素早く移植できたことを嬉しく思っています。HBM2対応のFPGAカード用にアプローチを最適化する作業はすでに終わっていましたが、OpenCLベースのユーザーには、最小限のインパクトで、BittWare のハードウェア上でoneAPIに移行する優れたパスが提供されます。

FPGA で HBM2 を使用することで、今回紹介したような特定のアプリケーションで大きなメリットを得ることができます。今回紹介したコードについて、より詳しい情報をお求めの方は、以下のフォームからお問い合わせください。また、BittWare の520N-MX FPGA カードについて、より詳しい情報をお求めの方は、以下のフォームからお問い合わせください。

このフォームに記入して、オープンソースのTARファイルをリクエストすることができます。 お渡しするコードには、オープンソースの凡例があります。

OneAPI 2D FFTをLinuxのダイナミックリンク、共有オブジェクトライブラリにコンパイルします。cmake . "と入力するだけで、そのライブラリが作成されます。

入力データを作成し、出力を検証またはプロットする簡単なNumPyスクリプトから、このライブラリを呼び出します。python runfft.py "と入力すると、グラフが表示されます。

上記のソフトウェアは、MX2100 FPGAをホストするBittWare 520N-MXカードを使って、Centos 8でIntel OneAPI tools Beta 10リリースをテストしました。このカード用にリリースされたOpenCLボードサポートパッケージは、OneAPIを動作させることも可能です。

"*"は必須項目

BittWare WebinarArkville Intel® Agilex™ FPGA を使用した PCIe Gen4 Data Mover Webinar Atomic Rules 社のArkville IP は、最近更新され、Intel をサポートしました。Agilex

BittWare パートナーIPクエリプロセッシングユニット(QPU)構築FPGA搭載アクセラレータは、PCIe Gen4スピードで保存データまたはストリーミングデータを照会、分析または再フォーマットします!Eideticomのクエリ

BittWare パートナーIP TimeServo IPコア 高性能システムタイマIP Atomic Rules社のTimeServo IPコアは、RTL IPコアで、以下のような役割を果たします。

BittWare パートナーIP NVMeブリッジ・プラットフォーム NVMeインターセプト AXI-Stream サンドボックスIP 計算機型ストレージ・デバイス(CSD)は、ストレージ・エンドポイントに計算機型ストレージ機能(CSF)を提供することができます。

45 South Main Street, Concord, NH 03301|コンコード、ニューハンプシャー州 603-406-6200 | 連絡先